11 Minute

O echipă formată din universități din SUA și o turnătorie națională a dezvăluit o nouă arhitectură de cip 3D monolitic care stivuiește memoria și calculul vertical, scurtând dramatic distanțele pe care le parcurg datele și promițând câștiguri majore pentru hardware-ul inteligenței artificiale. Prototipul — fabricat la turnătoria din SUA a SkyWater Technology — demonstrează cea mai mare densitate de cablaj vertical realizată până în prezent și arată avantaje clare și măsurabile de performanță față de proiectele convenționale 2D.

De ce stivuirea schimbă regulile jocului

Sistemele moderne de inteligență artificială solicită transferul unor volume uriașe de date între memorie și unitățile de procesare. Cipurile tradiționale plasează logica (unitățile de procesare) și memoria una lângă cealaltă pe același plan, obligând datele să parcurgă trasee lungi, adesea supraaglomerate. Acest blocaj — cunoscut pe scară largă ca „memory wall” (peretele memoriei) — limitează cât de rapid un cip își poate alimenta procesoarele, chiar dacă procesoarele devin tot mai rapide și numeroase.

Integrarea 3D monolitică adoptă o abordare diferită. În loc să distribuie componentele pe o suprafață plană, proiectanții construiesc mai multe straturi extrem de subțiri de circuite direct unul peste altul și le conectează prin cablaj vertical dens. Această arhitectură comprimă căile lungi care încetinesc mișcarea datelor, permițând ca memoria să se afle imediat lângă elementele de calcul care o folosesc cel mai mult. Rezultatul: comunicare mult mai eficientă, throughput crescut și consum de energie redus per operație. Implementarea interconectării verticale și a unei topologii optimizate de memorie poate conduce la îmbunătățiri semnificative în latență și eficiență energetică, beneficii esențiale pentru aplicațiile AI, edge computing și sisteme încorporate.

De la laboratoare la o turnătorie din SUA: cum a fost construit prototipul

Proiectul reprezintă o colaborare între cercetători de la Stanford University, Carnegie Mellon University, University of Pennsylvania, MIT și SkyWater Technology — cea mai mare turnătorie pure-play de semiconductori din SUA. Spre deosebire de eforturile 3D anterioare care stivuiau cipuri fabricate separat, această lucrare folosește un proces monolitic: fiecare strat nou este fabricat direct peste straturile anterioare într-un flux continuu de fabricație.

Unul dintre obstacolele tehnice pentru stivuirea monolitică este bugetul termic — temperatura maximă pe care o poate tolera un cip fără a deteriora straturile deja realizate dedesubt. Echipa a utilizat etape de procesare la temperaturi scăzute care păstrează circuitele existente, în timp ce permit depunerea și patternarea unor trepte adiționale deasupra. Acest control termic strict permite conexiuni de la strat la strat mult mai mici și mai dense decât interpozitoarele grosiere folosite în ansamblurile stivuite convenționale. Astfel, se pot obține via verticale (vias) cu diametre reduse, spațieri mai mici și rezistență electrică optimizată — factori esențiali pentru performanța și fiabilitatea interconectării verticale.

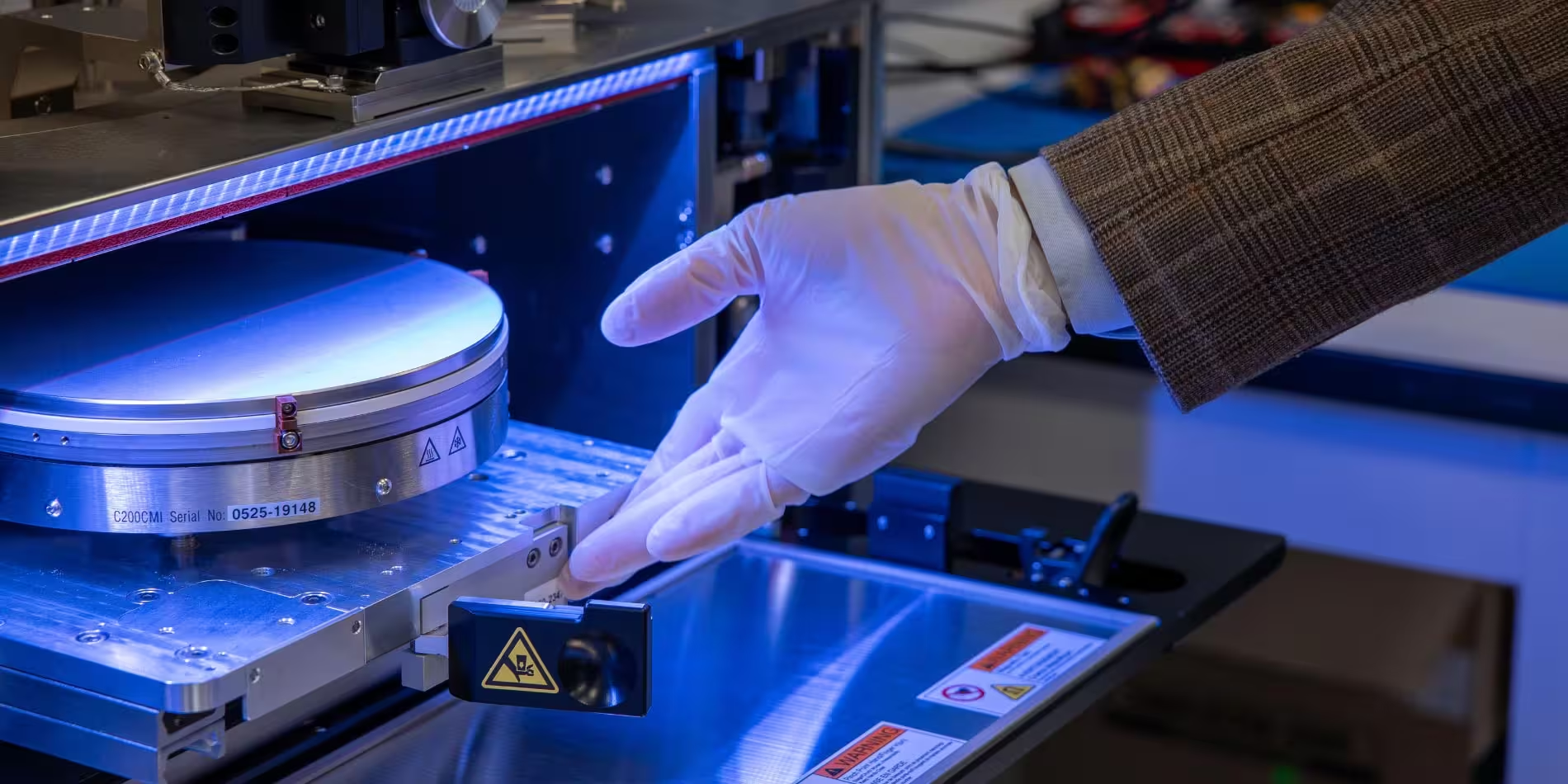

Pentru testarea noilor cipuri, cercetătorii au folosit o mașină specială, similară celei din imagine, pentru a realiza caracterizarea electrică automată a proiectelor pe o plachetă (wafer) de cipuri.

Finalizarea fabricației în turnătoria SkyWater din Minnesota reprezintă mai mult decât un jalon de producție — semnalează că arhitecturi 3D avansate pot fi traduse din prototipuri academice în procese compatibile cu fabricile comerciale domestice. După cum a explicat Mark Nelson, vicepreședinte la SkyWater Technology, în discuțiile despre proiect, permiterea producției la scară comercială pe sol american este esențială pentru reziliența lanțului de aprovizionare și pentru leadership-ul tehnologic național. Acest lucru are implicații pentru securitatea cibernetică, furnizarea hardware-ului AI și autonomia tehnologică, într-un context geopolitic în schimbare.

Performanțe măsurate și potențial simulat

Testele timpurii de pe hardware ale prototipului dezvăluie avantaje semnificative de performanță. Dispozitivul din prima generație a depășit echivalentele 2D, comparabile ca design, de aproximativ patru ori la anumite benchmark-uri. Când echipa a rulat simulări pentru proiecte mai înalte — cipuri cu mai multe niveluri stivuite de memorie și calcul — s-au observat câștiguri de ordinul unei mărimi (până la 10x) și, pentru anumite sarcini AI foarte dependente de lățimea de bandă memorie, îmbunătățiri de până la 12x.

Probabil cel mai convingător aspect este îmbunătățirea proiectului energie-întârziere (energy-delay product, EDP), o metrică combinată care echilibrează timpul de execuție și consumul de energie. Prin scurtarea dramatică a căilor de date și multiplicarea interconectărilor verticale, cipurile 3D monolitice pot reduce energia necesară per operație în timp ce cresc throughput-ul. Cercetătorii indică că există căi realiste către îmbunătățiri de 100–1.000x în EDP comparativ cu arhitecturile 2D curente, dacă se realizează stive mai înalte și proiecte optimizate. Această perspectivă include optimizări la nivel de microarhitectură, management termic integrat și telecomenzi EDA specializate pentru a valorifica pe deplin avantajele 3D.

Fundal științific: memory wall și limita miniaturizării

Două tendințe pe termen lung au limitat performanța cipurilor. În primul rând, sarcinile AI necesită seturi de date vaste și acces rapid la acestea. În al doilea rând, ruta tradițională a industriei celor semiconductori către performanță mai mare — micșorarea dimensiunilor tranzistorilor și plasarea unui număr mai mare de dispozitive pe un die plat — atinge limite fizice și economice dificile, denumite adesea „miniaturization wall” (peretele miniaturizării).

Stivuirea verticală abordează ambele constrângeri. În loc să se limiteze la comprimarea unui număr mai mare de tranzistori în același plan, proiectanții adaugă straturi suplimentare de funcționalitate în a treia dimensiune. Memoria poate fi distribuită pe întregul pachet, astfel încât nucleele de calcul să aibă acces local rapid la datele de care au nevoie. Arhitectura atacă astfel direct memory wall-ul, oferind în același timp o cale complementară la simpla scalare a tranzistorilor. În termeni practici, aceasta permite proiecte de tip near-memory computing și in-memory computing mai eficiente, reducând necesarul de acces la memorie externă și permițând latențe substanțial reduse pentru inferență AI și aplicații HPC.

De ce contează fabricația domestică din SUA

Faptul că întregul proces rulează într-o turnătorie din SUA are semnificație strategică. Lucrarea demonstrează că integrarea 3D monolitică avansată nu este doar o curiozitate de laborator, ci poate fi produsă folosind practici de fabricație disponibile pe teritoriul Statelor Unite. Pentru securitatea națională, competitivitatea industrială și cererea în creștere pentru hardware AI domestic, această traducere are importanță reală. Producția internă reduce dependența de lanțuri de aprovizionare externe și sporește controlul asupra proprietății intelectuale și a testării de securitate.

Dincolo de fabricație, există o dimensiune educațională și de forță de muncă. Tranziția către integrarea verticală va necesita ingineri și tehnicieni pregătiți să proiecteze, testeze și optimizeze sisteme 3D. Colaboratorii proiectului subliniază programe de formare și hub-uri multi-instituționale care deja sprijină implicarea studenților și cercetarea interdisciplinară, contribuind la pregătirea noii generații de proiectanți de cipuri pentru un peisaj hardware orientat vertical. Aceasta include cursuri în EDA 3D, management termic pentru pachete multi-strat și tehnici de testare și fiabilitate specifice cipurilor 3D.

Expert Insight

„Integrarea 3D monolitică reprezintă o reanaliză fundamentală a modului în care proiectăm sistemele de calcul,” spune Dr. Leila Martinez, arhitect de sisteme la un centru american de cercetare aerospațială. „Așezând memoria mai aproape de locul în care se face calculul, reduci atât latența, cât și consumul de energie. Pentru AI și sistemele spațiale — unde masa, alimentarea și performanța sunt strict limitate — aceasta poate fi transformatoare. Provocarea va fi scalarea fabricației menținând în același timp ratele de defecte și managementul termic sub control.”

Observația ei subliniază două realități: abordarea oferă câștiguri puternice de eficiență, dar ridică și noi constrângeri inginerești. Stivele verticale trebuie să gestioneze disiparea căldurii între nivele, să mențină randamentul la densități mai mari și să se integreze cu ecosistemele existente de proiectare și verificare. Implementarea cu succes necesită, de asemenea, dezvoltarea unor standarde de proiectare 3D, metodologii de testare la nivel de pachet și strategii de toleranță la defecte pentru a asigura fiabilitatea pe termen lung.

Provocări rămase și direcții de cercetare

Deși prototipul demonstrează îmbunătățiri notabile, rămân numeroase obstacole tehnice înainte ca cipurile 3D monolitice să devină omniprezente. Provocările cheie includ:

- Management termic: Căldura generată adânc în interiorul unui die stivuit trebuie îndepărtată fără a deteriora straturi sensibile; soluțiile pot combina disipatoare integrate, rutare termică optimizată și materiale cu conductivitate îmbunătățită.

- Randament și defecte: Integrarea mai strânsă înseamnă că defectele dintr-un singur strat pot afecta întregul cip; procesele de fabricație trebuie să atingă densități de defect scăzute pentru a menține costurile rezonabile.

- Unelte și metodologii de proiectare: Fluxurile de Electronic Design Automation (EDA) și uneltele de verificare trebuie să evolueze pentru a gestiona floorplanning tridimensional, rutare verticală și analize de timing între straturi.

- Fiabilitatea materialelor și interconexiunilor: Stabilitatea pe termen lung a via-urilor verticale și a materialelor depuse la temperaturi joase trebuie validată pentru cicluri de viață comerciale.

Grupuri de cercetare abordează activ aceste probleme. Simularea termică avansată, noi strategii de răcire, tehnici de atenuare a erorilor și progrese în procesele de depunere la temperaturi reduse fac parte din munca curentă. Partenerii din industrie, agențiile guvernamentale de finanțare și hub-urile inter-instituționale sprijină eforturile de a transpune progresele de laborator în produse fiabile. De asemenea, se investește în dezvoltarea infrastructurii de testare automată pentru wafer și în metode statistice de control al calității pentru a reduce impactul defectelor la scară.

Ce înseamnă aceasta pentru AI, spațiu și altele

Pentru dezvoltatorii de AI, integrarea mai strânsă între memorie și calcul poate permite rularea unor modele mai mari mai eficient, poate reduce costurile de operare în cloud și poate permite inferența mai capabilă la bord pentru sisteme edge și mobile. În contexte spațiale și de apărare, unde energia și volumul sunt la primă mână la economisire, cipurile 3D monolitice ar putea permite instrumentație mai performantă și procesare la bord în cadrul unor constrângeri stricte de masă și energie.

Anunțul semnalează, de asemenea, avansul unui ecosistem domestic mai larg de semiconductori: universități care pregătesc studenți, turnătorii care adaptează fluxurile de proces, și finanțare federală și industrială aliniată pentru a reduce dependența de fabrici externe. Luate împreună, aceste elemente conturează un viitor în care cercetarea din SUA se poate transforma mai rapid în hardware pregătit pentru producție.

Pe scurt, prototipul de cip 3D monolitic reprezintă un pas important. Nu elimină miraculos toate obstacolele inginerești, dar oferă o cale clară și fabricabilă către arhitecturi care pot depăși blocajele istorice. Pentru proiectanții de hardware AI, producătorii de cipuri și factorii de decizie politică, lucrarea subliniază o direcție promițătoare pentru câștiguri atât de performanță, cât și de eficiență energetică, prin reproiectarea celei de-a treia dimensiuni a cipului.

Sursa: scitechdaily

Lasă un Comentariu